FIR Filter Using Cadence for 16 Bit

Raja S.

1

, Kiruthika R.

2

, Mohammed Faizal N.

1

, Mohandas C. S.

1

,

Mugundha Kumar S.

1

and Muthu Kumar P.

1

1

Department of Electronics and Communication Engineering, SNS College of Technology, Coimbatore, Tamil Nadu, India

2

Department of Electronics and Communication Engineering, V.S.B College of Engineering Technical Campus,

Coimbatore, Tamil Nadu, India

Keywords: Finite Impulse Response (FIR), Very Large‑Scale Integration (VLSI).

Abstract: This project focuses on the design and implementation of a 16-bit Finite Impulse Response (FIR) filter using

the Cadence design environment. FIR filters are essential in digital signal processing due to their inherent

stability and precise linear phase characteristics, making them ideal for applications requiring high accuracy

and predictable performance. The design process begins with defining the filter specifications, including

cutoff frequency, order, and type. The coefficients are calculated using standard algorithms such as the

window method or Parks-McClellan optimization. These coefficients are then integrated into the hardware

design, ensuring optimal performance. Cadence tools are employed for schematic entry, simulation, and

layout generation. Detailed simulations are conducted to verify the functionality, frequency response, and

phase characteristics of the filter. Special attention is given to optimizing the filter design for power efficiency,

area minimization, and high-speed operation. The project also explores techniques to reduce hardware

complexity without compromising performance. The final implementation demonstrates effective signal

filtering, confirming the filter’s accuracy and robustness in handling 16-bit digital data. This work highlights

the versatility and efficiency of Cadence tools in developing high-performance digital signal processing

hardware.

1 INTRODUCTION

A FIR (Finite Impulse Response) filter is a type of

digital filter that processes signals by applying a finite

number of coefficients to the input signal. The output

of a FIR filter is determined by a weighted sum of the

current and past input values. FIR filters are widely

used in digital signal processing (DSP) applications

due to their inherent stability, linear phase response,

and simplicity in implementation. In this design, we

focus on implementing a FIR filter using Cadence, a

powerful suite of tools for the design, simulation, and

verification of integrated circuits (ICs) and systems.

Cadence provides a comprehensive environment for

simulating digital signal processing systems at

various abstraction levels.16-bit precision refers to

the bit-width of the filter’s coefficients and the data

precision used in the system. A 16-bit FIR filter can

process signals with a precision of 16 bits, allowing

for higher resolution and more accurate signal

processing. However, the design of such filters

involves considerations regarding quantization

errors, computational complexity, and memory

requirements.

2 EXISTING METHOD

The existing methods for designing a 16-bit FIR filter

using Cadence focus on efficiently generating filter

coefficients, quantizing them to fixed-point precision,

and ensuring the design meets performance

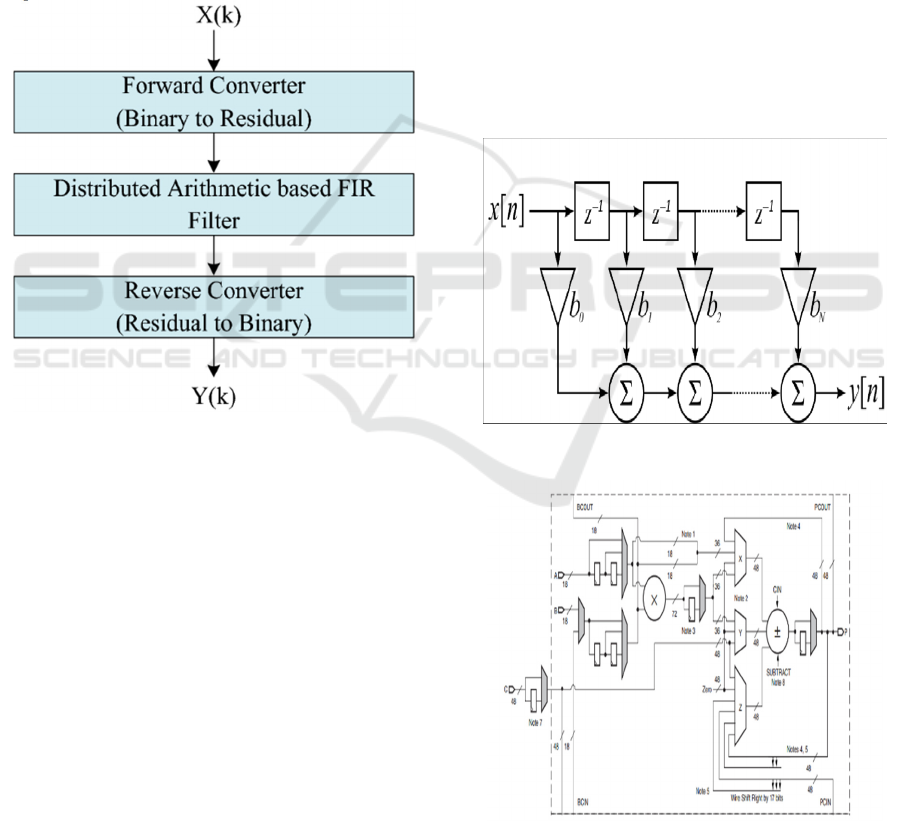

requirements. Figure 1 show the Existing Method.

The Windowing Method is often used for its

simplicity, applying a window function (like

Hamming or Blackman-Harris) to calculate the FIR

filter coefficients, though it may not yield optimal

performance in all cases. For more precise designs,

the Parks-McClellan Algorithm is employed, as it

minimizes the maximum error between the ideal and

actual frequency response, making it ideal for

applications demanding better stopband attenuation.

S., R., R., K., N., M. F., S., M. C., S., M. K. and P., M. K.

FIR Filter Using Cadence for 16 Bit.

DOI: 10.5220/0013914600004919

Paper published under CC license (CC BY-NC-ND 4.0)

In Proceedings of the 1st International Conference on Research and Development in Information, Communication, and Computing Technologies (ICRDICCT‘25 2025) - Volume 4, pages

461-464

ISBN: 978-989-758-777-1

Proceedings Copyright © 2026 by SCITEPRESS – Science and Technology Publications, Lda.

461

Additionally, the Least Squares Method can be

applied to minimize squared errors in the frequency

response. Once the coefficients are determined, 16-bit

quantization is performed, converting the filter's

coefficients and signals to fixed-point precision,

which involves careful handling of overflow,

rounding, and scaling to ensure accuracy. Cadence

simulation tools like Xcelium for digital simulation

and Spectre for mixed-signal simulation are used to

verify the filter’s performance before hardware

implementation. Finally, tools such as Stratus and

Virtuoso help in synthesizing the filter for FPGA or

ASIC deployment, ensuring that the design is

optimized for the 16-bit precision and system

requirements.

Figure 1: Existing method.

3 PROPOSED SYSTEM

Figure 2 show the proposed system aims to design

and implement a high-performance 16-bit FIR filter

using Cadence tools for efficient digital signal

processing. The system focuses on optimizing filter

architecture for low power consumption, high-speed

operation, and minimal hardware resource utilization.

The design incorporates an optimized Multiply-

Accumulate (MAC) unit, pipeline processing, and

parallel computation techniques to enhance

throughput. The FIR filter coefficients are stored

efficiently using registers or memory blocks, ensuring

precise filtering operations. The implementation is

carried out using Cadence Virtuoso for schematic

design, Spectre for circuit simulation, and RTL

Compiler for synthesis and optimization. The system

is tailored for FPGA or ASIC applications, making it

suitable for real-time DSP applications such as image

processing, biomedical signal filtering, and

communication systems. The proposed system

focuses on the design and implementation of a 16-bit

FIR filter using Cadence tools to achieve high

performance, low power consumption, and optimized

hardware utilization. The system employs an efficient

Multiply-Accumulate (MAC) unit with pipelining to

enhance speed and reduce latency. The filter

coefficients are stored in dedicated memory blocks to

ensure precision and stability in filtering operations.

The design is implemented using Cadence Virtuoso

for schematic capture, Spectre for circuit simulation,

and RTL Compiler for synthesis and optimization.

Additionally, advanced parallel processing

techniques and clock gating mechanisms are

integrated to improve computational efficiency. This

system is intended for real-time applications in

biomedical signal processing, communication

systems, and image processing, where accurate and

efficient digital essentials.

Figure 2: Proposed method.

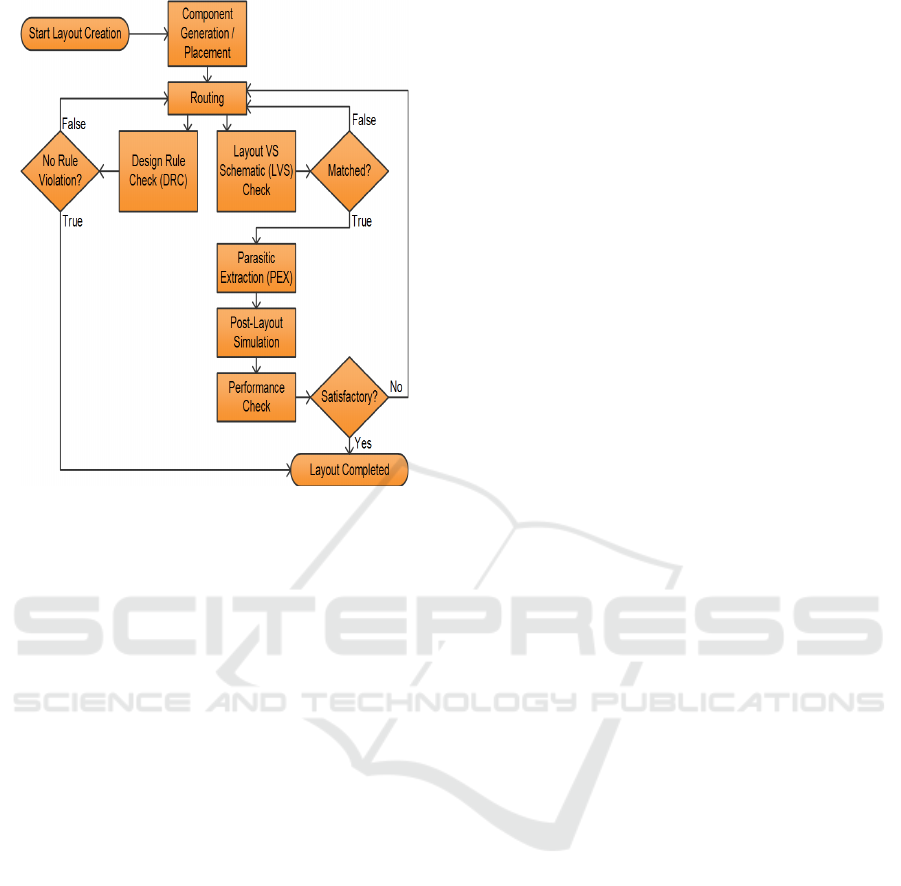

Figure 3: Flowchart of proposed method.

ICRDICCT‘25 2025 - INTERNATIONAL CONFERENCE ON RESEARCH AND DEVELOPMENT IN INFORMATION,

COMMUNICATION, AND COMPUTING TECHNOLOGIES

462

Figure 4: Circuit diagram of proposed method.

Figure 3 and 4 shows the Flowchart of Proposed

method and Circuit diagram of Proposed method

respectively.

4 RESULT

The result for a FIR filter using Cadence for 16-bit

precision typically includes several key outputs. One

of the primary results is the frequency response,

which can be visualized in terms of both magnitude

and phase. The magnitude response shows how the

filter passes or attenuates different frequency

components of the signal, while the phase response

indicates the amount of phase shift the filter applies

across frequencies. In the case of a 16-bit filter,

precision in frequency response is impacted by the bit

depth, which could influence the filter’s ability to

handle signals with high dynamic range.

5 CONCLUSIONS

In conclusion, designing a 16-bit FIR filter using

Cadence provides a robust framework for efficient

signal processing with an emphasis on precision,

performance, and resource management. The process

begins with defining the filter specifications,

followed by the calculation and quantization of

coefficients to 16-bit precision. Through simulation

using Cadence's tools, such as Spectre, the filter's

frequency response, impulse response, and

performance metrics like Signal-to-Noise Ratio

(SNR) and Total Harmonic Distortion (THD) are

analyzed.

6 FUTURE WORK

Future work involves integrating the FIR filter with

advanced signal processing systems. This could

include using the filter in combination with other

algorithms such as machine learning models for

automatic classification or multi-modal sensor data

fusion for applications like medical diagnostics,

communications, or audio processing. By integrating

these filters into more complex systems, their

capabilities can be expanded for a wider range of

practical applications.

REFERENCES

A. Sawant, A. Parashar, S. Saxena and S. Shukla, "RFID-

Based Smart Shopping Cart System", International

Journal of Engineering and Advanced Technology, vol.

9, no. 1, October 2019.

K. V. S. H. Gayatri Sarman and Srilakshmi Gubbala,

"Voice Based Objects Detection for Visually

Challenged Using Active RFID Technology",

International Conference on Cognitive Computing and

Cyber Physical Systems, pp. 170-179, 2022.

M. Sanap, P. Chimurkar and N. Bhagat, "SMART-smart

mobile autonomous robotic trolley", In 2020 4th

International Conference on Intelligent Computing and

Control Systems (ICICCS), pp. 430-437, 2020, May.

N.P. Challa, J.S.S. Mohan, V.S. Deepthi and S.

Rajeyyagari, "Smart Irrigation System using Internet of

Things", Proceedings of the 17th INDIACom; 2023

10th International Conference on Computing for

Sustainable Global Development INDIACom 2023.

P. Satheesan, S. Nilaxshan, J. Alosius, R. Thisanthan, P.

Raveendran and J. Tharmaseelan, "Enhancement of

supermarket using smart trolley", International Journal

of Computer Applications, vol. 975, pp. 8887, 2021

R. Raffik, D. Rakesh, M. Venkatesh and P. Samvasan,

"Supply Chain Control and Inventory Tracking System

using Industrial Automation Tools and IIoT", In 2021

International Conference on Advancements in

Electrical Electronics Communication Computing and

Automation (ICAECA), pp. 1-5, 2021, October.

Rudra Narayan Dash, Akshay Kumar Rathore, Vinod

Khadkikar, Ranjeeta Patel and Manoj Debnath, "Smart

Technologies for Power and Green Energy",

Proceedings of STPGE 2022, vol. 443, 2022.

S. Naveen, "Smart Shopping Trolley using QR Code and

ESP32Cam", Grenze International Journal of

FIR Filter Using Cadence for 16 Bit

463

Engineering & Technology (GIJET), vol. 8, no. 2,

2022.

T. Naveenprabu, B. Mahalakshmi, T. Nagaraj, N. K SP and

M. Jagadesh, "Iot based smart billing and direction-

controlled trolley", In 2020 6th International

conference on advanced computing and communication

systems (ICACCS), pp. 426-429, 2020, March.

V.P. Matta, R.S. Miriyala, K.V.S.H. Gayatri Sarman, M

K.V.S. Reddy, A M.V Pathi and C. Venkateswara Rao,

"Energy Efficient Smart Street Light System based on

Pulse Width Modulation and Arduino", 2023

International Conference on Computer Communication

and Informatics ICCCI 2023.

ICRDICCT‘25 2025 - INTERNATIONAL CONFERENCE ON RESEARCH AND DEVELOPMENT IN INFORMATION,

COMMUNICATION, AND COMPUTING TECHNOLOGIES

464